# Intusoft Newsletter

Personal Computer Circuit & System Design Tools

intusoft Copyright © Intusoft, All Rights Reserved

Issue #50 Sept. 1997 Tel. (310) 833-0710 Fax (310) 833-9658

In This Issue

**Schematics**

Reconfigurable

New TEST DESIGNER™

14 Viewlogic OEMs Intusoft

18 Inductor and Laser

20 Why IsSpice is Better!

22 New SMPS Book, New Models from Vendors

23 Who Has More Models?

Modeling

Modeling A Spark Gap

SPICE, ICAP for Protel

2

5

**NEW TEST DESIGNER**

ntusoft has released a revolutionary new simulationbased tool for analog and mixed-signal Failure Mode and Effects Analysis (FMEA) and Test Program Software (TPS) called development Test Designer™. Simply put, Test Designer automates failure analysis, fault diagnostics and isolation, and generates detailed fault trees and test strategy reports. The user can easily pair Continued on pg. 5

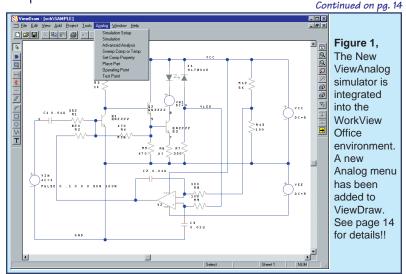

VIEWLOGIC TO OEM INTUSOFT'S TECHNOLOGY

Viewlogic Systems, Inc.

(NASDAQ: VIEW) has introduced ViewAnalog™, an analog and mixed-signal simulator developed by Intusoft, Inc. The simulator is

## **RECONFIGURABLE SCHEMATICS**

A long-standing problem in electrical and mechanical circuit design has been the conflict between the needs of the designer and the needs of production and manufacturing. The main method of conveying the designer's creation is the circuit schematic which is used to describe the behavior of the circuit as well as the details of how production will build the hardware.

The designer is concerned with creating a circuit that meets specifications. This is done chiefly through the use of various EDA tools, but mainly with circuit simulation. The designer must build multiple test configurations, add parasitic components and stimuli, and even include system elements in the simulation. A top-down design methodology, where different levels of abstraction are inserted for different components, is commonplace. Modeling electrical behavior often results in different representations for different test configurations. In general, the schematic becomes so cluttered with circuitry and data, that it must be redrawn for production, greatly raising the probability of a transcription error.

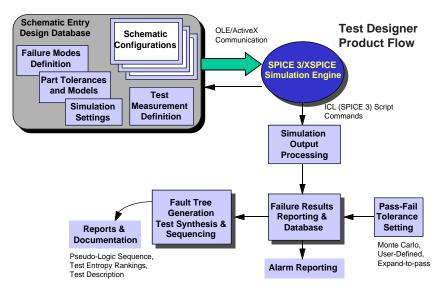

The need for a reconfigurable schematic capability becomes even more mandatory when we analyze the needs of the failure analysis and test program development software (Figure 2). In order to be effective, the simulation process can not become burdened with the bookkeeping intricacies of multiple schematic variations and analysis specifications. The designer must have a way to connect various stimuli and loads to core circuitry and to group different SPICE analyses and test measurements with each schematic configuration.

Until now, the best approach has been to hide these special configurations in subcircuits; for example a resistor's parasitic capacitance could be included in a subcircuit. While this approach works for hierarchical schematic entry and extending individual component models, it does not solve the problem of adding test equipment, different stimulus inputs, or dealing with multiple simulation scenarios.

A hardware test setup provides loads, voltage and current stimuli and instrumentation connections at specific points

Figure 2, A block diagram of the software system implemented to provide automated failure analysis and test program set development discussed in Test Designer, pg. 5.

on the Unit Under Test (UUT). When viewed in a broader context, the combination of the test setup circuitry and the UUT can be considered to be a circuit configuration in and of itself. Indeed, for simulation purposes, the test setup circuitry must be included as part of the circuit. Most Test Program Sets (TPSs) implement multiple setups during the testing sequence. This increases the simulation burden by requiring a separate schematic for every test setup.

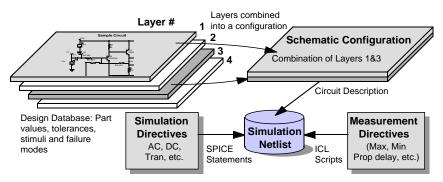

The system described by Figures 2 and 3 addresses the multiple test setup problem with a unique solution.

**Figure 3**, A unique reconfigurable schematic feature allows different schematic layers to be combined together in order to create various circuit configurations. Simulation and measurement directives are then added to create multiple test descriptions.

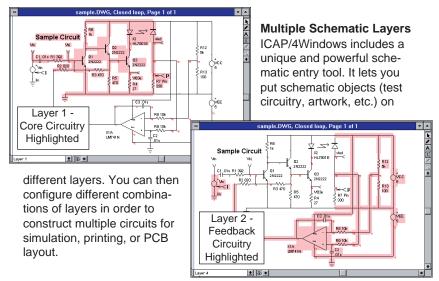

The setup/UUT combination is called a "circuit configuration". Every circuit configuration is composed of one or more schematic layers. A layer can be thought of as a transparency that overlays other transparencies such that as you view them, you see the completed schematic (Figure 4). Circuit nodes on the top layer connect with nodes on underlying layers as if the drawing were created on a single page. The schematic allows mixing and matching of layers to form the required circuit configurations. Any circuitry, elements, or documentation can be placed on any layer.

The user can assign each circuit configuration a name and a set of measurements. This pairing is referred to as a "test configuration". This methodology allows all of the different test configurations to be simulated in one batch operation.

Use of a layered concept in itself is not unique. It is generally used as a drawing management feature to remove complexity from the user's visual field, rather than making a multiplicity of configurations. While PCB layout tools have had a similar feature for some time, a configurable schematic has not been implemented (to the best of our knowledge). This is the first known graphical method which can solve the Test - Simulation bridge using a reconfigurable layered schematic approach.

Figure 4, A layered schematic composed of two layers; one holding the core circuitry and a second holding feedback/test-related elements.

# NEW TEST DESIGNER

Continued from page 1 multiple circuit configurations with various analyses and automated measurements to create "tests". The tests are simulated for each and every part failure mode. Test Designer then grades the performance of each test against pass/fail limits. Using the results, Test Designer then automatically sequences the tests into a fault tree.

Unique Features Redefine How The Test Engineer Works Test Designer includes a fully integrated schematic entry tool, extensive model libraries, state-of-the-art SPICE3 based analog and mixed signal simulator, a graphical data post processor, and a host of features that handle the failure analysis, test synthesis and reporting. All key data entry, analysis, and reporting features are **graphically driven**. You do not have to write any scripts or do any programming in order to define a model, a fault, a measurement, or a test.

The schematic entry tool integrates all of the relevant design and test information, fault analysis results, and test sequence data. You do not have to use several different programs from different EDA vendors. A single schematic database holds

#### Test Designer - Uses and Benefits

- Provides a framework for automatic test program set development

- Dramatically reduces the time to perform FMEA, diagnosis, and isolation

- Reduces fault tree sequencing time by orders of magnitude

- Thoroughly analyses your design; eliminates guesswork

#### Test Designer - Features

- All Operations Graphically Driven

- One Complete System: Schematic entry, Simulation, Libraries w/failure modes, failure diagnostics report, Fault tree generator, test sequence and ambiguity group reports

- User-defined soft, parametric and hard failure modes

- Automatic Fault tree sequencing

- Tracking of Test Configurations (circuit+analysis+measurement+pass/ fail tolerance)

multiple circuit configurations, multiple test setups, the fault properties for each part (including both topological and parametric value variations), the test definitions, the measurement definitions (Figure 5), tolerances, and all results.

Part faults are defined in a graphical manner using simple dialog entries. The proper netlist for each failed part scenario is generated automatically. You do not have to "code" any fault behavior. Over 10,000 part models are provided, and most include predefined failure modes. For example, all passive and active components use the U.S. Navy's CASS "standard" for the default failure modes.

Test Designer features an automated failure mode simulation capability. This allows you to easily define and simulate a series of Figure 5, Test Designer uses a Measurement tree to show the list of automated measurements. The measurements are paired with different circuit configurations to make "tests". Nominal measurement values are defined via an initial simulation. You can set asymmetrical pass/fail limits on each measurement. Tolerances can be set in absolute terms or percent.

| Main     Measurements     Faults     Vectors     Test Confi       Measurements     Closed <ul> <li>Closed</li> </ul> <ul> <li>Closed</li> <li>Closed</li> <li>Closed</li> <li>Closed</li> <li>Closed</li> <li>Closed</li> <li>Closed</li> </ul> <ul> <li>Closed</li> <li>Closed</li> <li>Closed</li> <li>Closed</li> </ul> <ul> <li>Closed</li> <li>Closed</li> <li>Closed</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Igurations OK Help Add Delete Edit Test Group |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| Closed Loop Standard  CoperatingPoint CoperatingPointAlam Coperat | Help<br>Add<br>Delete                         |

| Standard     OP     OP     OperatingPoint     OperatingPointAlam     TRAN     StdDev     Trace                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Add<br>Delete                                 |

| ⊕ OP     ⊕ OP     ⊕ OperatingPoint     ⊕ OperatingPointAlarm     ⊕ TRAN     ⊕ StdDev     ⊕ Trace                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Delete                                        |

| ⊕ OperatingPointAlarm     ⊡ TRAN     ⊕ StdDev     ☐ Trise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                               |

| in StdDev<br>⊟ Trise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Edit Test Group                               |

| E Trise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Edit Tol                                      |

component faults or other out-of-tolerance conditions. Test Designer automatically inserts each failure mode without altering the appearance of the schematic, performs the analysis, and removes the fault. The process is repeated, **without user-intervention**, until all of the faults have been inserted and simulated.

Test measurements from each simulation are setup with Measurement Wizards, while special reconfigurable report forms are used to review different views of the fault analysis and fault grouping data. Measurements such as peak-peak, maximum, rise time, propagation delay, etc., can easily be made.

An easy-to-read histogram meter shows the state of each resultant measurement, its pass/fail status, and indicates the degree that failed measurements are out-of-tolerance. Nu-

| Closed Loop 🔺             | 1          | Standard : TRAN |              |           | ,            |         |        |      |

|---------------------------|------------|-----------------|--------------|-----------|--------------|---------|--------|------|

| - Closed Loop             | Meter      | RefDes::Fail    | Measured     | Pass/fail | Min          | Nominal | Max    | 1    |

| E- OP                     |            | C2::Open        | -34.82f      | Fail      | 6.877n       | 7.356n  | 8.206n | - 1  |

| E-0P                      |            | Q2::opPC        | 743.8p       | Fail      | 6.877n       | 7.356n  | 8.206n | - 1  |

|                           |            | R11::Open       | 6.797n       | Fail      | 6.877n       | 7.356n  | 8.206n | - 1  |

|                           |            | R9::Open        | 6.865n       | Fail      | 6.877n       | 7.356n  | 8.206n | - 1  |

| ⊡ TRAN                    |            | C2::Short       | 7.449n       | Pass      | 6.877n       | 7.356n  | 8.206n | - 1  |

| i ⊡ StdDev                |            | C3::Open        | 7.586n       | Pass      | 6.877n       | 7.356n  | 8.206n | - 1  |

| 🖻 Trise                   |            | Q2::solder      | 7.718n       | Pass      | 6.877n       | 7.356n  | 8.206n | - 1  |

| V(16)                     |            | R12::Open       | 8.495n       | Fail      | 6.877n       | 7.356n  | 8.206n | - 1  |

| V(17)                     |            | X4::noLight     | 8.570n       | Fail      | 6.877n       | 7.356n  | 8.206n |      |

| V(18)                     | ║└╍╌┼╼╸    | C3::Short       | 8.588n       | Fail      | 6.877n       | 7.356n  | 8.206n |      |

| V(7)                      |            | R14::Open       | 8.593n       | Fail      | 6.877n       | 7.356n  | 8.206n |      |

|                           |            | R7::Open        | 8.669n       | Fail      | 6.877n       | 7.356n  | 8.206n |      |

| V18p_p                    |            | X5::openOut     | 8.686n       | Fail      | 6.877n       | 7.356n  | 8.206n |      |

| =-SafeToStart             |            | R10::Open       | 9.339n       | Fail      | 6.877n       | 7.356n  | 8.206n |      |

|                           | والمسال    | Q4::openBE      | 9.347n       | Fail      | 6.877n       | 7.356n  | 8.206n |      |

| <u> </u>                  | ┛╽└─────   | Q4::openC       | 14.93n       | Fail      | 6.877n       | 7.356n  | 8.206n |      |

| Report View Measurement 🔻 |            | R3::Open        | 20.47n       | Fail      | 6.877n       | 7.356n  | 8.206n |      |

| Measurement •             | •          |                 |              |           |              |         |        | Þ    |

| recision 4                | Set Limits | Copy to Clipbe  | oard Options | Save      | Variation No | Faults  | ▼ OK   | Help |

indicates which tests passed or failed.

merical results and test limits are also shown. Each measurement can be folded out to show the results for all faults (Fig. 6).

With all of the failure data in hand, Test Designer can sequence a fault tree, generate test strategy reports, and output test sequence pseudo-code (ATE independent), allowing you to quickly develop a test strategy for automated testing.

TPS design is accomplished graphically, by either automatically or manually selecting fault tree nodes from an ordered list of tests which are sorted by "entropy". The results for each fault tree design are saved with user names and descriptions. A fault tree can be designed all at once or in steps that gradually add more complex tests. The user can look at the results for each fault tree node, examine the underlying tests, and modify the test strategy (See Figure 7, next page).

You can enable or disable specific test vectors and part fault modes. This allows you to explore different test outcomes without having to repeat the circuit simulations.

Test results are output in several formats that can be imported in to the designer's ATE test programming language. These files contain the logical structure of the tests. The designer only needs to add the test equipment specific coding.

The combination of automated failure simulation and test sequencing is truly revolutionary. The time-savings over manual methods is DRAMATIC. This powerful capability extends SPICE well beyond its current single simulation-oriented boundaries, and provides a framework for automatic test program set design and FMEA.

With Test Designer, test strategies can be improved and debugged by enabling virtual production studies without the need to build a prototype or even wait until the design process has been completed.

Test Designer<sup>™</sup> is a vast improvement over current manual test development practices, and dramatically reduces the time-consuming process of test software development.

A detailed brochure on Test Designer, several technical articles and a demonstration version are available on the Intusoft web site. Test Designer is available immediately. It requires Windows 95 or Windows NT. Required product maintenance is 15% of the purchase price. Training classes are also available.

| Test Design: Fault Tree with Entropy                                                                                                                                                                                                                                                                                                   | Selection                                                                   |                                                                                                                                                                                                                                                                        | ×                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| Group sequence and selection                                                                                                                                                                                                                                                                                                           | Fault Tree Structure                                                        | Test Description                                                                                                                                                                                                                                                       |                  |

| Sequ         Test Group         Config           1         OperatingPoint         Closed L           2         OperatingPoint         Closed L           2         StdDev         Closed L           3         Trise         Closed L           4         V18p_p         Closed L           X-6         OperatingPoint         SafeToS |                                                                             | Step 1     @Vcc[i] hi 15, 16     OperatingPoint @Vcc[i] hi     IF test fails         goto Step 2     ELSE         goto Step 13     Test Description:         Test Fails if measurement i         above high limit     Measurement limits are:         Uter the step 10 | s                |

| Sequence 1  Pass O Fail                                                                                                                                                                                                                                                                                                                |                                                                             | High Limit = -87.40m<br>Low Limit = -95.92m                                                                                                                                                                                                                            | ▼                |

| Test Entropy Test Group                                                                                                                                                                                                                                                                                                                | ⊡ @Vee[i] lo 4, 4                                                           | Failure Selection                                                                                                                                                                                                                                                      | States-          |

| V(17) hi 0.6909 Operatii<br>V(16) hi 0.6730 Operatii IZ Save Trr<br>V(18) hi 0.6730 Operatii<br>@Vee[ 0.6365 Operatii<br>@Vee[ 0.5355 Operatii<br>@Vae] 0.5325 Operatii                                                                                                                                                                | ee Graph, ".TDT'' File<br>tailed test flow in".TDF'' File<br>withe TDF file | Cancel New Edit C His<br>C Ver<br>Help Percent of Failures Detected                                                                                                                                                                                                    | rtiary<br>togram |

**Figure 7, Test Designer Fault Tree Generation and Reporting**: Test design is accomplished in a graphical manner using the dialog above. Tests are sequenced using a probability based entropy algorithm that automatically builds the best fault tree (shown in the middle) from user-selected groups of tests (top-left). The resulting test descriptions and pass-fail ambiquity groups are shown on the right under Test Description.

Generated reports include the test description and pass/fail ambiguity groups (below, left) and the test sequence pseudo-code (below, right). The pseudo-code uses the logical structure of the test. The designer only needs to add the ATE specific coding.

|                                               | 🗃 ViewAnalogEditor - [FWD1843a.TDT]                                      | - 🗆 🗡 |

|-----------------------------------------------|--------------------------------------------------------------------------|-------|

| 🗃 ViewAnalogEditor - [FW/D1843a.TDF]          | 📴 Eile Edit Search Options Actions Window Help                           | _ 8 × |

| File Edit Search Options Actions Window Help  | File C:\Spice8\Circuits\Power\FWD1843a.<br>Fault Tree for: Safe-To Start | TDT   |

|                                               | 03 Aug 97, 15:46                                                         |       |

| Step 7                                        | if( Max V(3) == FAIL)                                                    |       |

| Max V(3) 10                                   | if( Max @V4[p] == FAIL)                                                  |       |

| IF test fails<br>replace Fail Ambiguity Group | {<br>if( Max @L2[i] == FAIL)                                             |       |

| ELSE                                          | ( · · · · · · · · · · · · · · · · · · ·                                  |       |

| replace Pass Ambiguity Group                  | if ( Max @Q1[icc] == FAIL)                                               |       |

| Test Description:                             | Q1::shortCE                                                              |       |

| Test Fails if measurement is                  | }<br>else                                                                |       |

| below low limit<br>Measurement limits are:    | {<br>X16::shortGD                                                        |       |

| High Limit = 2.822                            | }                                                                        |       |

| Low Limit = 2.816                             | }<br>else                                                                |       |

| Guard Band = 2.819m                           | {                                                                        |       |

| Fail Ambiguity Group, pFail = 0.5000          | D2::Short                                                                |       |

| L2::Open                                      | )<br>else                                                                |       |

| Pass Ambiguity Group                          | if( Max V(20) == FAIL)                                                   |       |

| D1::Open                                      | {<br>if( Max @L4[i] lo == FAIL)                                          |       |

| Test Ambiguity Group                          | 1 1                                                                      |       |

| L2::Open                                      | if( Max V(3) lo == FAIL)                                                 |       |

| Q1::shortCE<br>X16::shortGD                   | L2::0pen                                                                 |       |

| D2::Short                                     | else                                                                     |       |

|                                               | {<br>D1::Open                                                            |       |

| Step 8<br>@L1[i] 2, 2                         | }                                                                        |       |

| Max @L1[i]                                    | }<br>else                                                                | -     |

|                                               |                                                                          | Þ     |

|                                               |                                                                          |       |

Christophe BASSO, consultant, SINARD, FRANCE

Spark gaps or Electrical Surge Arrestors (ESAs) are highly nonlinear devices whose function is to stop transient surges on DC or AC power-supply lines. Such transients can be caused by lightning strikes, motor starts, etc. In other cases, spark gaps can also be used repetitively in ignition-type circuits. A spark gap is made of two electrodes that face each other across a short distance. The gap is fill with air or an inert gas like argon or neon. If the voltage applied to the ESA is below its striking voltage (or avalanche potential), the current flowing through the ESA is close to zero. Once the striking voltage is attained, the voltage across the ESA suddenly collapses to a value called the glow voltage. If the current still increases, the ESA voltage decreases further to a level called the arc voltage, where it stays until the surge passes. At this point, the ESA stays conductive until its current falls below a sustaining value in a manner similar to a thyristor.

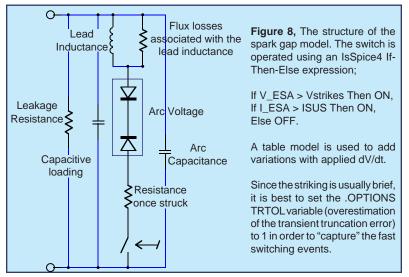

Modeling such a component with SPICE can be done in several ways [1, 2]. For the sake of efficiency, we have used a macro-modeling technique. It consists of assembling SPICE primitives in a group to describe a complex electrical function. Figure 8 depicts the general ESA model we have adopted.

In the OFF state, the voltage-controlled switch is open and only a leakage current circulates in the ESA. The switch stays

OFF until the voltage across the ESA rises up to the striking voltage. At this point, the switch is immediately driven ON and the network made of the back-to-back zener diodes and the series resistance is applied across the ESA terminals. At this point, the voltage collapses to the arc value and the current starts to rise. When the surge passes, the ESA current decays until the sustaining value is reached and the switch opens. In the first model in Table 1, the glow transition is not taken into account, and neither is the dV/dt applied to the ESA. The netlist uses standard SPICE3 elements combined with an IsSpice4 If-Then-Else behavioral element (BARC, in Table 1 below) which performs the arcing action.

In the second model, shown in Table 2, a behavioral piecewise linear (PWL) table function is used to account for the dV/dt applied to the device. The PWL table converts the absolute value of the applied slope in coefficients that, when multiplied by VTHRES, will increase the final BARC level. The PWL values in the PWL\_001 model are extracted from a curve which depicts the ignition voltage versus the applied dV/dt. The curve generally appears parabolic when the x axis uses a log scaling. The effect is modeled by the source BARC 15 0 V=ABS(V(1,2)) > {VTHRES} + {VTHRES} \* V(33) ?... V(33) increases VTHRES by a ratio defined by the manufacturer's curves.

.SUBCKT SPARK 1 2 {VTHRES=90 VARC=10 ISUS=500M RNEG=-0.5 LPL=130N + RPL=2.5K CPAR=1P CARC=3P} \* Subcircuit parameters: \* VTHRES = VOLTAGE AT WHICH THE SPARKGAP STRIKES \* VARC = VOLTAGE ACROSS THE SPARKGAP ONCE STRUCK \* ISUS = CURRENT UNDER WHICH THE ARC IS STOPPED \* **RNEG** = NEGATIVE RESISTANCE ONCE STRUCK \* LPL = LEAD INDUCTANCE, usually in nanoHenries \* RPL = FLUX LOSS ASSOCIATED WITH LPL, usually in kohms \* **CPAR** = GAP CAPACITANCE \* CARC = ARC CAPACITANCE Table 1, The IsSpice4 netlist for a surge arrestor model. The **VDUM 1 10** operation does not depend on the LPL 10 11 {LPL} applied dv/dt. Since the striking is RPL 10 11 {RPL} very fast, it is strongly advised CPAR 12 {CPAR} that you set TRTOL variable in RLEAK 1 2 10MEG the .OPTION statement to 1. RNEG 11 17 {RNEG} DTRK1 12 17 DCLAMP (.OPTIONS TRTOL=1). This will DSRK2 12 16 DCLAMP force SPICE to be more vigilant in CARC 1 16 {CARC} the vicinity of transitions. X1 16 2 13 SWITCH BARC 15 0 V=ABS(V(1,2)) > {VTHRES} ? 10V : The user-defined parameters in + ABS(I(VDUM)) > {ISUS} ? 10V : 10N the model are described at the RDEL 15 13 10 top in bold. CDEL 13 0 10P .MODEL DCLAMP D BV={VARC} .ENDS

.SUBCKT A81-A230X 1 2 {VTHRES=230 VARC=10 ISUS=500M LPL=130N RPL=2.5K + CPAR=1.4P CARC=3P} **VDUM 1 10** Table 2, The IsSpice4 netlist for a LPL 10 11 {LPL} RPL 10 11 {RPL} spark gap model with the dV/dt CPAR 12 {CPAR} variation effect added. The **RLEAK 1 2 10G** parameters shown are for the DTRK1 12 11 DCLAMP SIEMENS A81-A230X ESA. DSRK2 12 16 DCLAMP CARC 1 16 {CARC} X1 16 2 13 SWITCH BARC 15 0 V=ABS(V(1,2)) > {VTHRES} + {VTHRES} \* V(33) ? 11V : + ABS(I(VDUM)) > {ISUS} ? 11V : 10N RDEL 15 13 10 CDEL 13 0 10P A1 35 33 PWL 001 RA1 33 0 10MEG \* INPUT SLOPE CALCULATION V/us \*\*\* BDIFF 40 0 V=V(1,2) EDIFF 30 0 0 31 100MEG **RDIFF 30 31 1MEG** CDIFF 40 31 1UF ECONV 32 0 30 0 -1U BABS 35 0 V=ABS(V(32)) < 10M ? 10M : ABS(V(32)) > 1K ? 1K : ABS(V(32)) .MODEL PWL\_001 PWL(XY\_ARRAY=[10.0M 1.0M 100.0M 86.0M 1.0 217.0M + 10.0 521.0M 100.0 956.0M 1.0K 1.6] INPUT\_DOMAIN=10M FRACTION=TRUE) .MODEL DCLAMP D BV={VARC} .ENDS

Obtaining the PWL points is easy. For the Siemens A81-A230x, the threshold voltage of the spark gap is 230V. The curve is flat up to 10kV/s or 10mV/us. For shallow slopes, up to 10mV/us, the first coefficient will be very low, between 1mV and zero. The third point on the curve is for 10E6V/s or 1V/us. At this point, the threshold voltage is 280V. The coefficient is simply: ABS(230-280)/230=0.217, or in the PWL table format: 1.0, 217M. For 10E7V/s or 10V/us, the curve gives a threshold of 350V: ABS(230-350/230)=521M  $\longrightarrow$  10, 521M and so on. To adapt the model to a particular spark gap device, you only need to enter a few parameters (variables in curly braces) found in the manufacturer's technical specifications.

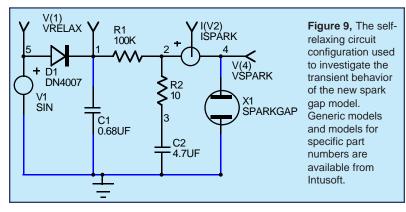

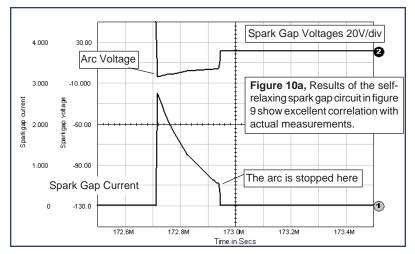

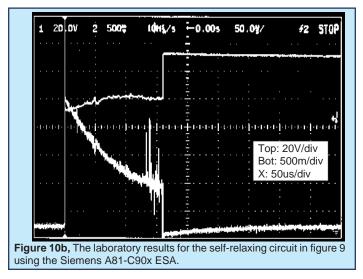

The first IsSpice4 test is made using a self-relaxing configuration as depicted by Figure 9. Since the phenomena are very fast, you will need to view the raw non-interpolated SPICE data (internal calculated data points) simulated by IsSpice4 and not the interpolated (.PRINT) data specified by the TSTEP parameter in the .TRAN statement. Thanks to IntuScope, ICAP's waveform analysis tool, you can easily explore both types of data. Figure 10a depicts the results given by IsSpice4. Figure 10b shows an oscilloscope hardcopy of the actual tested circuit.

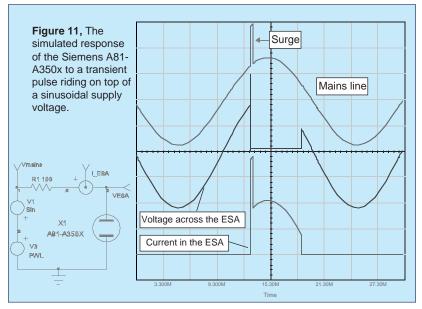

A second test is run using the spark gap as a real surge arrestor. The power mains supply a device protected by an

ESA. A 1µs transient (PWL source: PWL 0 0 13ms 0 13.001m 600 13.3ms 600 13.301m 0) has been added to the sinusoidal (SIN 0 320 50) supply voltage in order to trigger the ESA. The results simulated by IsSpice4 are shown on Figure 11.

The model presented here runs fast and converges without difficulties. Although the model accounts for several nonlinear effects, it is still a simplification of the complex phenomenon associated with spark gap ignition and arcing.

Note that a warm or cold cathode fluorescent (CCFL/HCFL) lamp could be easily derived from this model. In the next *Intusoft Newsletter* we will explore such a model and give examples.

A pre-made set of surge arrestor models for various manufacturer's devices is available as part of the new Mechatronics model library. The library will be available November 3, 1997. More details on the Mechatronics library will be available in the next newsletter.

#### References

- An Electrical Surge Arrestor (ESA) Model For Electromagnetic Pulse Analysis, Rockwell International Electronics Operations, IEEE Transactions on Nuclear Science, Vol. NS-24, No 6, December 1977

- [2] A SPICE model for simulating Arc Discharge load, M. NARUI, 1991 IEEE Industry Applications Society Annual Meeting, Volume II.

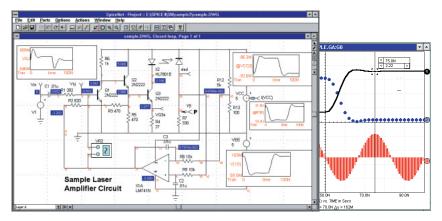

## NEW ICAP FOR VIEWLOGIC

Continued from page 1 available as part of Viewlogic's WorkView Office<sup>™</sup> Version 7.4 suite of Windows EDA tools. ViewAnalog, which targets the design and development of analog and mixed-signal circuits, is tightly integrated with Viewlogic's ViewDraw schematic capture tool. ViewAnalog is sold exclusively by Viewlogic as an OEM product. A similar product, called *ICAP<sup>™</sup>* for Viewlogic, is available directly from Intusoft. However, the Intusoft version does not support Viewlogic's powerful Fusion technology for mixed-mode simulation.

Dave Orecchio, Director of Marketing for Viewlogic's Systems Group, stated "After reviewing their (Intusoft's) technology for analysis of analog designs, Viewlogic selected Intusoft for the ViewAnalog product. The technical expertise of Intusoft, coupled with customer demand for strong technology in ViewAnalog, convinced us that a strategic relationship and OEM agreement with Intusoft would benefit the broad range of both companies' customers."

"We are excited about this new agreement," said Charles Hymowitz, Vice President of Intusoft. "With Viewlogic, we can reach a whole new market with our state-of-the-art software. Both Viewlogic and Intusoft are using OLE/ActiveX technology to create a previously unattainable level of integration. Viewlogic customers will now have the easiest-to-use, most sophisticated analog/mixed-signal simulation environment; one which is far superior to previous offerings".

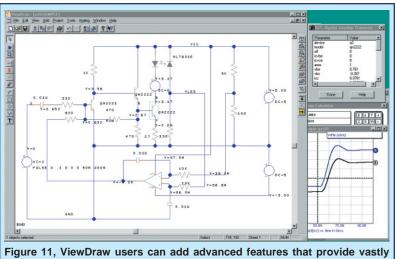

Figure 11, ViewDraw users can add advanced features that provide vast improved integration with analog and mixed signal simulation.

In addition to its native analog and gate-level digital simulation capabilities, ViewAnalog supports the BSIM3 version 3 and SOI MOSFET models. The tool also supports SPICE libraries with over 10,000 analog and digital parts, as well as C-code subroutine modeling, RF device models and a unique power supply designer's library.

The interactive operation of ViewAnalog frees the ViewDraw user from traditional batch-style SPICE analysis. In addition, SPICE part browsing and model editing allows easy design entry along with interactive cross-probing of the schematic. High-performance algorithms provide very fast simulation and improved convergence for difficult circuits. ViewAnalog's advanced features include: behavioral modeling, sweeping of any circuit variable; native mixed mode and gate-level, 12-state timing simulation; interactive waveform cross-probing, automatic curve-family generation, and real-time display of voltages, currents and power dissipation. ViewAnalog can analyze switch-mode power supplies, mixed-signal ASICs, RF communication systems, PCB interconnects, control systems, and mixed electrical/mechanical systems.

Viewlogic Systems, Inc. is a worldwide supplier of electronic design automation software. For more company and ViewAnalog product information, see the Viewlogic internet home page at http://www.viewlogic.com.

ICAP for Viewlogic will be available October 14, 1997 from Intusoft or your local dealer. Options include RF, Power, and Mechatronic (Mechanical/Hydraulic) SPICE model libraries.

### **SPICE** for **Protel** Users

The next system in the ICAP<sup>™</sup> series has been announced; *ICAP* for Protel. For Protel Schematic<sup>3™</sup> users, the wait for seamless integration of SPICE 3 based simulation is over! ICAP uses the EDA Client/Server architecture, Protel's powerful integration technology and OLE (Object Linking and Embedding) to transparently integrate the powerful set of ICAP/4 analog and mixed signal capabilities into the Protel Schematic<sup>3</sup> schematic environment. *ICAP* for Protel will ship September 29, 1997. Contact Intusoft, your local Intusoft dealer, or your local Protel dealer for more information. There are two Deluxe options; RF and Power. They each include the SpiceMod modeling software, Vendor Supplied IC models, SPICE Reference Books (A SPICE Cookbook & SPICE Applications Handbook), and either the RF Device or Power Supply Designer's model library.

If you've been looking to upgrade your evaluation version of SPICE, or are thinking about getting started with simulation, we'd like to suggest a system that's easy-to-learn but powerful enough to tackle all of your design jobs. It's called **ICAP/4Rx** and it's a complete circuit simulation system that includes everything you need to simulate all types of system, board, and IC level designs.

The ICAP/4Rx system strikes a perfect balance between **ease-of-use** and **power**. It has the power to handle tough designs, and removes the steep learning curve associated with using SPICE. And it does this without compromising power as some other electronic workbench systems do, and at the lowest cost possible.

#### Simulation Environment

- Full Schematic Entry and waveform analysis tools

- Unlimited circuit size

- Powerful and PROVEN IsSpice4 simulator (SPICE 3 and XSPICE-based)

- All major SPICE analyses: AC, DC, Operating Point, Transient, Fourier, Temperature and Parametric "What-If" analyses

- · Interactive analyses and parameter sweeping

- · Real time waveform display

#### SPICE Features

- Comprehensive SPICE Libraries (3000+ parts) includes all vendor supplied models, <u>all models unencrypted</u>

- Advanced Behavioral Modeling: Math expressions, If-Then-Else, Table & Laplace models, AHDL Models, and BSIM3 version 3

Advanced Convergence Algorithms

# SPICE POWER AND EASE-OF-USE!

ICAP/4Rx is an integrated circuit simulation system including our 5th generation schematic entry tool, proven IsSpice4 simulator, waveform post processor, and SPICE model libraries. It is reduced in complexity in order to provide you with the easiest simulation environment to use.

#### New Graphical User Interface

- Easiest-to-Use Integrated Schematic-SPICE environment

- No need to learn SPICE syntax, all functions graphically driven

- Advanced Waveform Cross-probing; Waveforms can be shown directly on the schematic or in IntuScope with a single mouse click

- New "Parametric Sweep" tool painlessly generates curve families

- · Integrated Symbol Editor; Uses .BMP and .WMF files

- · Custom attribute dialogs for each part; on-the-fly model/subcircuit editing

#### Wizards

- · Analysis Wizard alleviates the need to type SPICE statements

- Convergence Wizard solves common simulation problems for you

#### Other Features

- No Hardware Protection Key

- Compatible with virtually all schematic capture programs

- Grows with You!! Rx is Upgradable to our full ICAP/4Windows system

#### Benefits To New Users

- New schematic interface makes it easy to get results instead of headaches

- Integrated schematic-simulator solution makes you instantly productive

- Eliminates SPICE syntax problems

- Our mature 4th generation SPICE 3F program, IsSpice4, is timetested and gives you accurate answers you can trust

- Powerful waveform analysis with multiple windows and cursor measurements gets the most out of simulation

- Reduced complexity makes using ICAP/4Rx effortless

### **Cost Difference Upgrade** to ICAP/4Windows

ICAP/4Windows includes a number of key features that are not found in ICAP/4Rx. But as with ALL Intusoft software you can upgrade for the price difference.

- Native Mixed Mode simulation

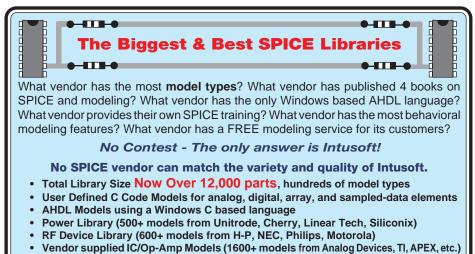

- Full ICAP/4 Model Libraries (12,000+ models)

- More advanced IsSpice features (Interactive Sweeping, VB/OLE Interfaces)

- More advanced analyses (noise, distortion, sensitivity)

- Monte Carlo analysis

- Circuit Optimization

- Ability to add Design Validator<sup>™</sup> and Test Designer<sup>™</sup> options

- Failure Analysis

### NEW MODELS FROM VENDORS

A variety of new vendor supplied models are included in this issue of the *Intusoft Newsletter* floppy. PWM ICs, TI, Maxim and AD Op-Amps, Polyfet RF Power Mosfet, and Zetex discretes, to name a few. Models for Coilcraft Inductors and lasers, are also included on the floppy and are discussed below in more detail.

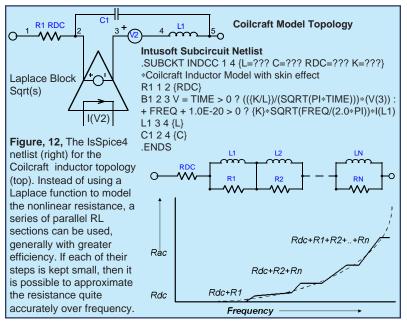

Figure 12 shows an equivalent schematic of an inductor as described by Coilcraft (www.coilcraft.com) in their DOC158-2 app note [1]. The coilcraft topology uses the square root of s, implemented using a Laplace expression, to model the skin effect. Skin effect can also be modeled using a network of linear components [2]. For example, Magnetics Designer uses a series set of parallel RL elements as shown in Figure 12. This technique is more efficient and less prone to simulation timestep problems than the Laplace approach.

In any case, the IsSpice4 syntax representing the coilcraft topology is shown in Figure 12. R1 is the inductor dc resistance, B1 forms an equivalent circuit for the AC inductor resistance. The If-Then-Else expression defines a frequency dependent voltage which simulates the frequency dependent resistance due to the conductor skin effect. L1 is the low frequency inductance. This is measured at a low frequency where the distributed winding capacitance is negligible. C1 is the distributed

uted winding capacitance. Dielectric and permeability effects are not directly accounted for in this model.

[1] Modeling Inductors with SPICE, Coilcraft, Cary, Illinois, Tel.847-639-6400 [2] "SMPS Simulation With SPICE 3", Steve Sandler, McGraw-Hill 1997.

### QW-Laser Model Using Rate Equations

Pablo V. Mena, Steve. A. Javro, Sung Mo Kang Copyright 1997 The Board of Trustees of the University of Illinois. All rights reserved. Reprinted with Permission from The Board of Trustees of the University of Illinois.

The quantum-well (QW) laser model is implemented as an equivalent circuit composed of both parasitic elements (series and parallel) and one of two possible intrinsic cavity models.

Table 3, The IsSpice4 netlist for a quantum-well laser. QW-LASER INTRINSIC CAVITY SUBCIRCUIT Each qw cavity subckt has the name qwlas<a><b>. <a><b> identify the model. - a = model number = 1: one-level rate-equation model 2a: two-level rate-equation model with SCH recombination 2b: two-level rate-equation model w/o SCH recombination - b = level number = 1: full logarithmic gain 2: simplified logarithmic gain 3: gain linearized about optical transparency gain linearized about threshold Example: QWLAS11 One-level rate-equation with Full Log Gain .SUBCKT QWLAS11 P N PF {NE=1E12 N=2 NE2=1E12 NW2=1 ETAI=1 + LAMBDA=850E-9 NW=1 VACT=1E-17 GAMMA=0.1 VGR=1E8 TP=3E-12 + ETAC=0.35 NO=1E24 NTH=1.25E24 GO=1E5 M=1 EPS=1E-23 TN=1E-8 AP=0 + A=1E8 B=1E-16 C=0 AB=1E8 BB=1E-16 CB=1E-40 BETAA=0 BETAB=1E-6 + BETAC=0 VBARR=1E-16 TCAPT=1e-12 TEM=1e-9 CJO=0 MPOW=0.5 VJ=1 + FC=0.5 DELTA=1e-60 DEL2=0 TF=1} D1 P NT1 D1MOD IC1 P NT1 {1.60219E-19\*NW\*VACT\*NE/(2\*ETAI\*TN)} VT1 NT1 N 0 D2 P N D2MOD IC2 P N {1.60219E-19\*NW\*VACT\*NE/(2\*ETAI\*TN)} BR1 P N I={2\*AP\*TN}\*I(VT1) + {4\*ETAI\*B\*TN^2/(1.60219E-19\*NW\*VACT)}\*I(VT1)\*I(VT1) + {8\*ETAI^2\*C\*TN^3/(1.60219E-19\*NW\*VACT)^2}\*I(VT1)\*I(VT1)\*I(VT1) BS1 P N I={LAMBDA\*TP\*1.60219E-19\*NW\*GAMMA\*VGR\*GO/(ÉTAI\*ETAC\*6.6262E-34\*3E8)}\* + (V(M)+{DEL2})\*(V(M)+{DEL2})\*LN({DELTA}+{2\*A\*ETAI\*TN/(1.60219E-19\*NW\*VACT)/ + (A\*NO+B\*NO^2+C\*NO^3))\*I(VT1)+{4\*B\*(ETAI\*TN/(1.60219E-19\*NW\*VACT))^2/ + (A\*NO+B\*NO^2+C\*NO^3)}\*I(VT1)\*I(VT1)+{8\*C\*(ETAI\*TN/(1.60219E-19\*NW\*VACT))^3/ + (A\*NO+B\*NO^2+C\*NO^3)}\*I(VT1)\*I(VT1)\*I(VT1)/(1+{EPS\*GAMMA\*LAMBDA\*TP/(ETAC\*VACT\* + 6.6262E-34\*3E8)}\*(V(M)+{DEL2})\*(V(M)+{DEL2})) RPH M 0 1 CPH M 0 {2\*TP} BR2 0 M I=({2\*ETAI\*ETAC\*TN\*6.6262E-34\*3E8\*BETAA\*A/(1.60219E-19\*LAMBDA)}\*I(VT1)+ + {4\*ETAI^2\*ETAC\*TN^2\*6.6262E-34\*3E8\*BETAB\*B/((1.60219E-19)^2\*LAMBDA\*NW\*VACT)}\* + I(VT1)\*I(VT1)+ {8\*ETAI/3\*ETAC\*TN/3\*6.6262E-34\*3E8\*BETAC\*C/((1.60219E-19)/3\*LAMBDA\* + (NW\*VACT)^2)}\* I(VT1)\*I(VT1)\*I(VT1))/(V(M)+{DEL2}) BS2 0 M I={TP\*NW\*GAMMA\*VGR\*GO}\*(V(M)+{DEL2})\*LN({DELTA}+ + {2\*A\*ETAI\*TN/(1.60219E-19\*NW\*VACT)/(A\*NO+B\*NO^2+C\*NO^3)}\*I(VT1)+ {4\*B\*(ETAI\*TN/(1.60219E-19\*NW\*VACT))^2/(A\*NO+B\*NO^2+C\*NO^3)}\*I(VT1)\*I(VT1)+ + {8\*C\*(ETAI\*TN/(1.60219E-19\*NW\*VACT))^3/(A\*NO+B\*NO^2+C\*NO^3)}\*I(VT1)\* + I(VT1)\*I(VT1))/(1+{EPS\*GAMMA\*LAMBDA\*TP/(ETAC\*VACT\*6.6262E-34\*3E8)}\*(V(M)+{DEL2})\* + (V(M)+{DEL2}))-{DEL2} BPF PF 0 V=(V(M)+{DEL2})\*(V(M)+{DEL2}) .MODEL D1MOD D IS={1.60219E-19\*NW\*VACT\*NE/(2\*ETAI\*TN)} N={N\*TF} .MODEL D2MOD D IS={1.60219E-19\*NW\*VACT\*NE/(2\*ETAI\*TN)} N={N\*TF} TT={2\*TN} + CJO={CJO} M={MPOW} VJ={VJ} FC={FC} .ENDS

## WHY ISSPICE4 IS BETTER!!! - [Simula

IsSpice4 provides a quantum leap in performance over other analog and mixed mode simulators. It is the first commercially available version of SPICE based on Berkeley SPICE 3F and Georgia Institute of Technology's XSPICE.

IsSpice4 allows you to explore circuit performance by interactively running different analyses and sweeping any circuit variable. With the ability to simulate electrical, sampled-data, mechanical, physical, thermal, and other systems, **IsSpice4 is the ONLY true interactive native mixed mode SPICE 3 based simulator.** The advanced features of IsSpice4 allow all types of applications to be simulated: switch mode power supplies, mixed signal ASICs, RF communication systems, interconnects, control systems, and mixed mechanical/physical systems.

Intusoft has spent thousands of man-hours improving SPICE. And although IsSpice4 is based on SPICE 3, Intusoft has greatly enhanced the program over and above the public domain version and added more features, an interactive interface, superior analysis and model support, and improved convergence algorithms - all for a price no one can match. IsSpice4 is simply the best and most affordable SPICE program on the market today. Just take a look at some of its features:

#### State-of-the-Art Operation

- Native mixed mode simulation IsSpice4 includes an event driven simulator that supports mixed analog, digital and DSP circuits.

- Interactive Operation IsSpice4 operates interactively, and frees you from the restrictive batch style of older SPICE simulators.

- Interactive Command Language Comprehensive set of functions for batch style control of the simulator

- NEW VISUAL BASIC SCRIPTING Drive IsSpice4 using VB scripts from popular programs like Excel.

- NEW OLE INTERFACE Develop your own OLE/ActiveX interfaces

#### Built-in Models

- Elements: Resistors, Capacitors, Inductors, Coupled Inductors, Transmission Lines, Diodes, BJTs, JFETs, MOSFETs (Level 1-8), GaAs Mesfets, Switches, and Boolean logic expressions.

- Digital and AHDL Models: Digital primitives, State Machine, Frequency Divider, RAM, Sampled-Data Filters, Nonlinear VCOs, Laplace Equations

- Behavioral Modeling: In-line Equations, Table models, If-Then-Else

#### Advanced Models

- HDL Models and C Subroutines; Create your own models based on a powerful nonproprietary HDL using C

- · Support for nonelectrical applications and top-down system design

- Three types of digital/mixed mode modeling

- · Lossy (distributed) transmission lines with frequency dependent losses

- MOS: BSIM1, BSIM2, BSIM3 version 3.1 and SOI MOSFET models

- MESFET: Statz, Curtis-Enttenburg, Parker-Skellern, and HEMT models

| Analysis Support                                                                                                                                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AC, DC, transient, noise, Fourier, distortion, DC/AC sensitivity, Pole-Zero                                                                                               |

| analyses, and Temperature variations on individual elements                                                                                                               |

| <ul> <li>Monte Carlo Analysis, Circuit Optimization/Performance Analysis</li> <li>NEW DESIGN VALIDATOR™ for automatic design verification</li> </ul>                      |

| NEW TEST DESIGNER™ Failure Analysis and Software Test Set Design                                                                                                          |

|                                                                                                                                                                           |

| Additional Interactive, AHDL & Mixed Mode Features                                                                                                                        |

| Real-time Display of voltages, currents and power dissipation                                                                                                             |

| <ul> <li>Simulation Scripts: a robust scripting language that allows simulation<br/>breakpoints and loops of different analyses to be run as a test procedure.</li> </ul> |

| <ul> <li>Interactively run analyses without having to edit the netlist or restart the</li> </ul>                                                                          |

| simulator, add, delete, or rescale waveforms on the real-time display                                                                                                     |

| <ul> <li>Digital Simulation: IsSpice4 includes a 12 state digital logic simulator and<br/>models with timing information</li> </ul>                                       |

| <ul> <li>Sweep parameters one at a time or in groups with great ease</li> </ul>                                                                                           |

| Start, stop, pause, change, or resume any analysis on demand                                                                                                              |

| Use C code subroutines & AHDL models based on XSPICE                                                                                                                      |

| Convergence and Speed Improvements                                                                                                                                        |

| Automatic Gmin stepping/Source stepping algorithms                                                                                                                        |

| New Pseudo-Transient algorithm                                                                                                                                            |

| Improved Predictor-Corrector, Latency, and Bypass algorithms                                                                                                              |

| <ul> <li>Improved program defaults</li> <li>Special Circuit Debugging Options</li> </ul>                                                                                  |

| Full Gear Integration option                                                                                                                                              |

| European Manager Live and                                                                                                                                                 |

| Compatibility Heasure Hode:                                                                                                                                               |

| True OLE Integration with popular schematic entry programs                                                                                                                |

| DID YOU KNOW INTUSOFT WAS THE FIRST?                                                                                                                                      |

| The following is a list of capabilities that Intusoft introduced to the                                                                                                   |

| analog simulation world.                                                                                                                                                  |

| Paraistense 2                                                                                                                                                             |

| SFICE 2 Models for. ISBTS, luses, lasers, vacuum lubes,                                                                                                                   |

| generic template models, dual gate Mosfets, SC filters, neural<br>networks, digital gates, RF beads, IBIS buffers, saturable                                              |

| cores, and PWMs (using the state space approach)                                                                                                                          |

| Start Pause Besume About F                                                                                                                                                |

| Products/Features: 32-bit Version of SPICE for DOS, integrated                                                                                                            |

| schematic entry dedicated to SPICE, SPICE 2G model generation software, XSPICE extensions, parameter passing,                                                             |

| OLE/Visual Basic Interface for SPICE                                                                                                                                      |

|                                                                                                                                                                           |

| A SPICE FOR EVERYONE!                                                                                                                                                     |

| Affordability is the hallmark of Intusoft's products. With our new                                                                                                        |

| ICAP/4Rx, ICAP/4Windows, and ICAP/4Macintosh software, all affordably priced, there's an IsSpice that's just right for you.                                               |

| anordably priced, mere's an isopice mars just right for you.                                                                                                              |

### NEW SMPS BOOK AVAILABLE

Intusoft is pleased to announce the availability of an important NEW SPICE reference book. The book, entitled *SMPS SIMULATION WITH SPICE3*, is published by McGraw-Hill. It is authored by Steve Sandler, a well known authority in the power electronics and simulation arena. The book is a **MUST HAVE for every power circuit designer** who is using or thinking of using SPICE. It includes information on magnetics and power supply modeling, simulation, and circuit design techniques. There is also a chapter from renowned magnetics expert Rudy Severns on **Modeling Magnetics**

(inductors, transformers, nonlinear core models, and reluctance modeling). Topics in the new book include:

- EMI Filter Design: Using SPICE to calculate harmonic content

- Buck-Flyback Topology Converters: Average vs. Transient Modeling for Voltage/Current Mode control

- Linear Regulators: Control Loop Stability

- DC-AC Conversions: State machine modeling, Sine ROMs

- Improving Simulation Speed: Tips for Power Supply Designers

The book is available from Intusoft or your local Intusoft dealer immediately.

## NEW MODELS FROM VENDORS

#### Continued from page 19

The first cavity model is based on the two basic rate equations, one for QW carrier concentration, the other for photon density in the active region. The second cavity model includes a third rate equation for carriers in the barrier, or confinement, layers adjoining the QWs. Unimolecular, radiative, and Auger recombination are each accounted for in the model. Furthermore, one of four different gain terms can be chosen. These terms include both logarithmic gain expressions as well as linearized ones. Finally, the parasitic elements of the model can account for series resistance, additional series diode effects, and shunting resistance or capacitance. Unlike a typical model implementation within SPICE, the laser model is included as a subcircuit. (Table 3).

The inductor models and the laser models are posted on the Intusoft web site, www.intusoft.com, for interested parties.

[1] P. V. Mena, S. M. Kang, T. A. DeTemple, "Rate-equation-based laser models with a single solution regime," Journal of Lightwave Technology, vol. 15, no.4, pp. 717-730, April 1997

· More models created every day